在大流量测量系统中,为了完成传播时间测量、超声回波信号采集、数据分析以及图形显示等功能,往往需要多 CPU 进行协同处理,这将导致整个系统显得臃肿繁杂,文中系统采用单片 FPGA 并在其内部例化 MicroBlaze 软核处理器,应用结果表明,该系统不仅保证了测量精度,同时还使系统运行更加稳定可靠。

0.引言

超声波流量计无可动部件,可以实现非接触高精度测量,具有量程宽、无压损、成本对口径变动不敏感等优点,在石油化工、污水处理、工业及生活用水等领域有着广泛的应用前景,同时也是大口径水流量测量的最佳技术选择 。

由于复杂的外界环境干扰,特别是在大口径水流量测量中,干扰会使超声波接收信号发生波动,轻的会产生静态漂移问题,严重的可能出现测量错误,甚至无法完成测量工作。为了采集高频超声波信号,并进行数字信号处理,以提高测量精度,一般流量计都设计有 CPLD 或 FPGA 来对超声信号进行采集,并用 DSP 完成数字信号处理器,有的还需要用 ARM 等处理器来实现人机接口,若再加上外围配套芯片将使整个系统显得相当复杂。文中采用单片高性能 FPGA 以及其内部 MicroBlaze处理器软核来实现以上芯片所有功能,这将使整个系统更加简洁、稳定、可靠。

1.时差法流量测量原理

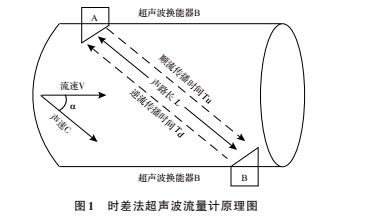

时差法超声波流量计原理是根据超声波信号顺逆流传播时间之差来计算流量 ,即首先根据顺流传播时间和逆流传播时间之差计算出流速,再根据测量断面面积计算出流量 。如图 1 所示。

超声波换能器 A 和 B 为同一声路中的一对换能器,当其中一个用作发射换能器时,另一个则作为接收换能器。Tu 为顺流传播时间,Td 为逆流传播时间。所测断面瞬时流量公式:

Q = S × | L | 1 | 1 | ||||

× | − | ||||||

2 cos α | |||||||

Tu | Td | ||||||

其中 α 为流速与超声波传播路径的夹角,L 为声路长,S 为管道面积。

2. MicroBlaze 软核处理器

MicroBlaze 是 Xilinx 公司基于 FPGA 的 32 位 RISC 哈佛架构软核嵌入处理器,可提供高级架构选项,如存储器管理单元 (MMU)、指令和数据端缓存、可配置的流水线深度和浮点单元 (FPU) 等,同时具有 70 多种用户可配置选项,可实现几乎所有处理器用例,用户根据需要可裁减为很小的微控制器,也可通过添加 IPCore 实现运行 Linux 的高性能计算密集型系统。

与传统独立 CPU 相比,软核嵌入处理器在可重构建、可定制等方面特别具有优势 。由于软核嵌入处理器实现在 FPGA 内部,可有效地提高可靠性、减少芯片数FPGA 实现的 SOPC( 可编程单芯片系统 ),在体积、重量、功耗、成本等各方面均有较大的优势 。

Xilinx 为 FPGA 开发提供了功能强大的 ISE设计平台,ISE 平台为 MicroBlaze 提供了专用的处理器硬件设计工具 XPS(Xilinx Platform Studio) 和软件开发与调试工具 SDK(Software Development

Kit)。由于嵌入处理器最终要与硬件逻辑电路共同存在 FPGA 内部,所以顶层设计要在 ISE 内进行, XPS 是针对软核和硬核处理器的设计工具,对软件的设计和调试,主要在 SDK 中完成。

3.系统结构

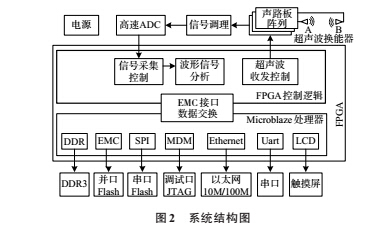

由单片 FPGA 构成 SOPC 系统,主要由以下几部分组成。

电源:包括系统工作电源和超声波高压发射电源。

超声收发电路:包括高速 ADC、信号调理和声路板阵列。

人机交互接口:包括以太网、串口和触摸屏。

4)FPGA:包括控制逻辑、双端口 RAM、MicroBlaze 软 核 处 理 器 及 其 外 围 配 套 电 路 DDR3、 FLASH 和 JTAG 调试口。

用 Xilinx 公 司 Spartan®-6 FPGA 型 号 为XC6SLX45。MicroBlaze 处理器通过 FPGA 逻辑单元控制超声波信号的发射、接收、信号采集和波形信号分析,根据分析结果通过流量积分算法获得当前流体流量,并将测量结果通过串口和以太网发出,用户可通过触摸屏查看当前和历史测量数据,也可通过调试界面查看系统和各声路工作状态。

MicroBlaze 处理器主频配置为 100MHz,使用 DDR3 内存,串口 FLASH 用于存放 FPGA 配置、 BootLoader 程序和用户程序,并口 FLASH 用于存放系统历史数据,JTAG 除用作 FPGA 硬件逻辑和软件程序调试外还具有向 FLASH 下载配置参数和程序代码功能。MicroBlaze 具有专用配置向导,需要使能处理器浮点单元、指令和数据高速缓冲存储器和整数乘法器,以提高流速、流量等算术运算效率。

4.波形数字信号分析

在时差法超声波流量计中,超声波传播时间测量大都采用阈值比较法 ,但在外界出现干扰时,此法将导致测量误差,严重的可能出现测量错误,通过对超声波和噪声信号进行分析比较,提出了基于零点分析的传播时间测量方法。

当接收换能器接收到超声波信号时,会在其电极两端产生并输出电信号 y(t),用数学公式表示为:

y ( t ) = r ( t ) cos ( 2πf 0t + φ)

式中:r(t) 为关于时间 t 的流体对超声波调制函数; f0 为换能器固有谐振频率;Φ 为初始相位(为了讨论方便,设初始相位为零)。

当 t=(2k+1)/4f0(k 为整数)时,y 的值为零,该时刻点称为零点,超声波在流体中传播时,环境噪声主要影响调制信号 r(t) 部分,对 cos(2πf0t) 部分没有影响,因此零点不受调制信号 r(t) 的影响,即不受信号 y(t) 的幅值波动影响。

根据这一特性,把 cos(2πf0t) 的第一个零点作为判断接收超声信号到达的标志,就可以很好地解决阈值比较法中由于环境噪声而导致到达时刻错判问题。

波形数字信号分析模块根据此原理,使用 Verilog HDL 硬件描述语言对这一过程进行解析,完成传播时间测量和波形状态分析,可为下次测量优化范围门、信号增益和滤波设置,使系统一直保持在良好的工作状态。

5.FPGA 内部数据交互

MicroBlaze 处理器需要把控制命令及流量测量相关参数传递给 FPGA 控制逻辑单元,同时也要接收从 FPGA 控制逻辑单元上传的数据,上传数据包括声路传播时间、超声波形采集数据和波形信号分析数据。用于流量测量的超声波频率在 1MHz 左右,为保证信号分析精度,使用 12 位高速 ADC 采集超声波信号,其采样速率最高达到 80MSPS,这就需要一个高效的数据交互机制。

当控制逻辑单元完成测量后将向 MicroBlaze 处理器发送中断信号,MicroBlaz 则调用中断处理程序,读取数据,并将下次测量参数传送给控制逻辑单元。通过分析这一过程,完全可以将 FPGA 控制逻辑单元看作 MicroBlaze 的一个外设存储器,是一个能同时被 MicroBlaz 处理器和 FPGA 控制逻辑单元访问的双端口 RAM。

EMC(External memory controller)IP 核, 即外部存储器控制器,可为 SRAM、Flash、PSRAM/或 Cellular RAM 等存储器提供接口。MicroBlaze通过 EMC 使得存储器的接口连接和控制变得轻松简便,本系统中 FPGA 控制逻辑单元和并口 Flash 都使用了 EMC 核,EMC 核由 XPS 工具软件免费提供,需由用户根据具体存储器类型和时序设置 EMC 核中相关参数。

6. BootLoader

与 ARM 等嵌入式系统的启动过程所不同的是,FPGA 必须先将内部硬件配置完成之后,才能运行程序代码 。虽然可以直接将程序代码例化到FPGA 内部 Block RAM(简称 BRAM)中运行,但是由于 FPGA 内部 BRAM 资源非常有限,当遇到大型系统设计时 ( 如带 TCP/IP 协议栈 ),就必须使用外部 RAM 来储存程序代码,这就需要设计规模较小的 BootLoader 程序来完成用户程序的引导,将用户程序从 Flash 中读取并转移到外部 RAM 中运行(如 DDR3)。

BootLoader 与处理器、外设类型和外设地址分配等系统硬件密切相关 , 不具有通用性。本系统选择基于 SPI 接口的串行 FLASH 的配置方式,在SDK 工具上对 BootLoader 进行开发。

SDK 工 具 自 带 有 SREC BootLoader 工 程 模板,使用此模板还需要做以下工作:

1) 调整串行 FLASH 中用户程序映射地址根据 download.bit 硬件配置文件大小调整用户程序在串行 FLASH 中所存放的映射地址,在 blconfig.h 中 其 宏 定 义 名 为 FLASH_IMAGE_ BASEADDR。

2) 须初始化 BootLoader 到内部 BRAM SDK 工 具 中 执 行 Program FPGA 时 选 择BootLoader 的 elf 格式文件,命令完成后将生成新的嵌入有 BootLoader 的 download.bit 文件。

3) 用户程序必须为 srec 格式用户程序编译前,需要在编译设置中,对 Post-Build Steps 增加以下内容: mb-objcopy -O srec *.elf *.srec

其中“*”应用具体用户程序名替代,这样在生elf 格式文件同时将生成 srec 格式文件。

后 使 用 iMPACT 软 件 工 具 将 新 生 成 的 download.bit 文件和 srec 格式文件一起生成 MCS文件,可直接下载到串行 FLASH 中运行。需要注意的是,当在 MCS 中添加 srec 格式数据文件

时,该数据文件起始地址应与 FLASH_IMAGE_ BASEADDR 宏定义一致。

7 .结论

由单片 FPGA 构成的 SOPC 系统,软件升级和配置修改都非常灵活,特别是数据采集和信号分析能力,极大地提高了时差法超声波流量计的计量精度。基于 MicroBlaze 软核处理器所设计开发的时差式多声路超声波流量计已经通国家水大流量计量站检定,并达到了 1 级标准,流量误差小于 0.5%。